1 Avoid mixed clock edges

Guideline 01 Avoid using both positive-edge and negative-edge triggered flip-flops.

If must use both positive-edge and negative-edge triggered flip-flops, then

1) model the worst-case duty cycle of the clock accurately in synthesis and timing annalysis

2) document the assumed duty cycle in the user documentation.

Guideline 02 If must use a large number of both positive-edge and negtive-edge triggered FFs,

separate them into different modules.

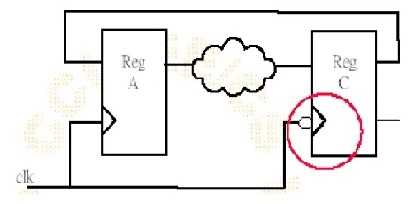

Bad example - Mixed clock edges

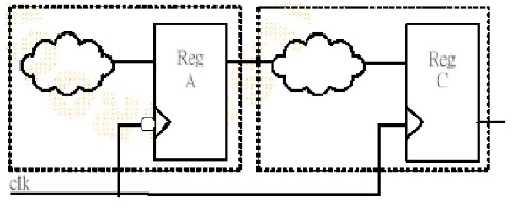

Better example - Negative-edge and positive-edge FFs are separated

原文:http://www.cnblogs.com/mengdie/p/4385661.html