四、用TimeQuest对DAC7512控制器进行时序分析

在对某个对象下时序约束的时候,首先要能正确识别它,TimeQuest会对设计中各组成部分根据属性进行归类,我们在下时序约束的时候,可以通过命令查找对应类别的某个对象。

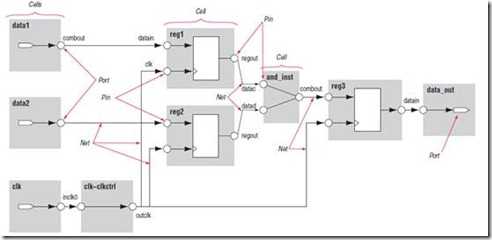

TimeQuest对设计中各组成部分的归类主要有cells,pins,nets和ports几种。寄存器,门电路等为cells;设计的输入输出端口为ports;寄存器,门电路等的输入输出引脚为pins;ports和pins之间的连线为nets。具体可以参照下图(此图出自Altera Time Quest的使用说明)。

下面我们按照本文第三部分用TimeQuest做时序分析的基本操作流程所描述的流程对DAC7512控制器进行时序分析。建立和预编译项目的部分相对简单,涉及到的也只是QuartusII的一些基本操作,这里我们就不再做具体的叙述。主要介绍如何向项目中添加时序约束和如何进行时序验证。首先建立一个名称与项目top层名字一致的sdc文件,然后按照下面的步骤添加时序约束。

1. 创建时钟

添加时序约束的第一步就是创建时钟。为了确保STA结果的准确性,必须定义设计中所有的时钟,并指定时钟所有相关参数。TimeQuest支持下面的时钟类型:

a) 基准时钟(Base clocks)

b) 虚拟时钟(Virtual clocks)

c) 多频率时钟(Multifrequency clocks)

d) 生成时钟(Generated clocks)

我们在添加时序约束的时候,首先创建时钟的原因是后面其它的时序约束都要参考相关的时钟的。

基准时钟:

基准时钟是输入到FPGA中的原始输入时钟。与PLLs输出的时钟不同,基准时钟一般是由片外晶振产生的。定义基准时钟的原因是其他生成时钟和时序约束通常都以基准时钟为参照。很明显,在DAC7512控制器中,CLK_IN是基准时钟。我们用下面的命令来创建这个基准时钟:

1 create_clock -name CLK_IN -period 40 -waveform {0 20} [get_ports {CLK_IN}]

其中,create_clock是创建时钟的命令,后面是命令的各种选项。其中-name CLK_IN选项给出了时钟的名字,即CLK_IN。-period 40给出了时钟的周期,即40ns。-waveform {0 20}给出了时钟的占空比,即50/50。最后的[get_ports {CLK_IN}] 是嵌套的tcl命令,给出了CLK_IN对应的port,实际上也就是CLK_IN的输入引脚。

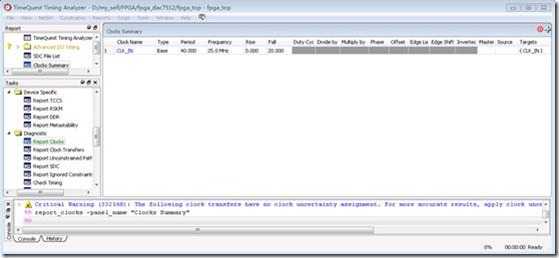

在sdc文件里添加上述命令后,在quartusII里编译设计,然后通过tools –> TimeQuest Time Aanlyzer命令打开TimeQuest。在TimeQuest的Tasks窗口,找到Report Clocks,双击之,TimeQuest就会在右边主窗口给出设计中已成功添加的时钟信息。如下图所示,可以看到CLK_IN,其类型为基准时钟,周期为40ns,频率为25MHz,targets项为CLK_IN,即表示这个时钟是连接在CLK_IN端口上的。这说明上面create_clock的命令已经在设计中正确创建了时钟CLK_IN。

实际上对于create_clock命令,我们可以通过quartus II的帮助系统(http://quartushelp.altera.com/current/),查找它的语法。在QuartusII的帮助里,可以查找到:

|

Syntax |

create_clock [-h | -help] [-long_help] [-add] [-name <clock_name>] -period <value> [-waveform <edge_list>] [<targets>] |

另外,帮助系统里有很详尽的关于该命令的描述,并且给出了各种使用的范例。不仅仅是这一个命令,所有的命令都可以在帮助系统里找到。如果看到一个陌生的命令,或者不知道命令该如何使用,那么最好的办法就是在帮助系统里查找该命令。

PLL时钟:

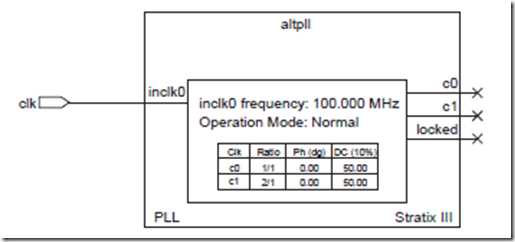

上面我们创建了基准时钟。下面我们创建PLL输出的时钟。在Altera的FPGA中,PLL电路是通过ALTPLL的IP库被添加到设计中的。下图是一个典型的ALTPLL的结构图。

从图上可以看到,当我们选定了基准时钟和PLL的参数以后,PLL的输出c0和c1的参数就随之确定了。所以在QuartusII环境下,可以通过一个简单的命令让软件自动生成PLL输出的时钟的时序约束。

derive_pll_clocks

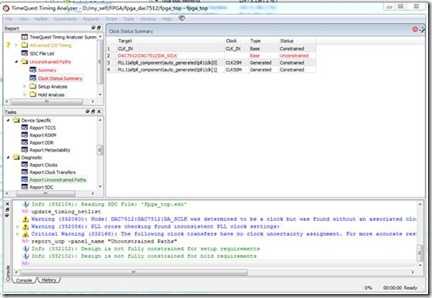

这个命令会自动创建PLL输出的C0和C1的相关时序约束。同样的,在sdc文件里添加该命令,然后编译,在TimeQuest里查看时钟信息。如下图所示,derive_pll_clocks在系统里添加了两个时钟,PLL1|altpll_component|auto_generated|pll1|clk[0]和PLL1|altpll_component|auto_generated|pll1|clk[1]。可以看出,时钟是按“PLL层次结构+时钟端口名字”的规则命名的。时钟的类型为created clock,周期频率是在PLL里设定好的。duty_cycle为50/50。Clock source为PLL1|altpll_component|auto_generated|pll1|inclk[0],实际上就是我们之前定义的CLK_IN。derive_pll_clocks会自动搜索时域网络并创建PLL的输出时钟。也可以使用create_generated_clock命令。

derive_pll_clocks的命令格式为:derive_pll_clocks [-create_base_clocks] [-use_tan_name]

选项[[-create_base_clocks]自动为pll生成输入时钟,[-use_tan_name],在默认的情况下,时钟的名字为输出时钟的名字。

derive_pll_clocks命令调用create_generated_clock命令以在pll的输出时钟上生成衍生时钟,create_generated_clock的源是pll的输入时钟引脚,在调用derive_pll_clocks命令之前或之后,我们必须手动的为pll生成一个作为其输入时钟的基础时钟,们如果我们未定义这个输入时钟,那么报告中就不会有pll的输出时钟,分析仪会给出警告:

The master clock for this clock assignment could no be derived.

clock:<name of pll output clock pin name> was not created.

所以使用<-created_base_clocks>选项自动为pll生成输入时钟约束。

可以将drive_pll_clocks命令放在你的sdc中,以使得derive_pll_clocks命令能自动的检测pll的任何变化,当使用derive_pll_clocks命令,将自动对pll进行约束。

用derive_pll_clocks命令创建PLL相关的时钟很是方便,但不好的地方就是,时钟的命名太过复杂,我们在添加与此时钟相关的时序约束时,就必须用这种名字很长的时钟,容易出错,且可读性也差。所以建议还是采用create_generated_clock命令来创建PLL的时钟 create_generated_clock命令的语法如下,可以从quartusII的帮助系统里找到每个参数的详细解释。

|

Syntax |

create_generated_clock [-h | -help] [-long_help] [-add] [-divide_by <factor>] [-duty_cycle <percent>] [-edge_shift <shift_list>] [-edges <edge_list>] [-invert] [-master_clock <clock>] [-multiply_by <factor>] [-name <clock_name>] [-offset <time>] [-phase <degrees>] -source <clock_source> [<targets>] |

可以用下面的命令来创建PLL的两个时钟C0和C1。我们把时钟命名为CLK25M和CLK50M,source clock为CLK_IN。

create_generated_clock -name CLK25M -source CLK_IN -duty_cycle 50.000 -multiply_by 1 -master_clock {CLK_IN} [get_pins {PLL1|altpll_component|auto_generated|pll1|clk[0]}]

create_generated_clock -name CLK50M -source CLK_IN -duty_cycle 50.000 -multiply_by 2 -master_clock {CLK_IN} [get_pins {PLL1|altpll_component|auto_generated|pll1|clk[1]}]

用这两个命令创建的时钟与derive_pll_clocks命令创建的时钟的本质是一样的,只是给时钟定义了不同的名字。当然我们也可以用derive_pll_clocks中对时钟的命名方式来使用create_generated_clock命令。同样的,可以按照上面的方法,在TimeQuest里查看创建时钟的结果,如下图所示。

注意,derive_pll_clocks,若没有选择[-create_base_clocks],此命令不会为驱动pll的input clock ports create base clocks,若选择此项,就会自动为pll的输入端口创建基准时钟。

到此为止,我们创建了PLL的基准时钟以及PLL输出的两个时钟CLK25M和CLK50M。

DA_SCLK时钟:

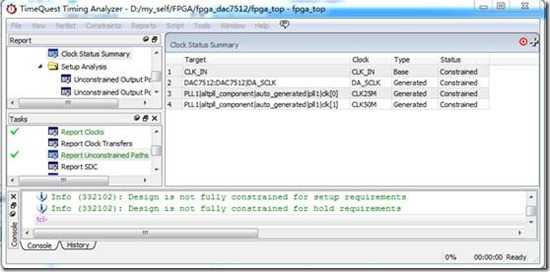

在TimeQuest的Tasks窗口里,选择Report Unconstrained Paths命令,TimeQuest会报告出所有需要下约束但实际并没有约束的情况。在Report里的Unconstrained Path列表下,我们可以查看这个报告。双击Clock Status Summary,就可以在主窗口看到所有时钟的情况。见下图,很明显,软件辨识出DAC7512模块下的DA_SCLK为时钟信号,但是我们并没有对该时钟添加约束,所以用红色将这个时钟显示了出来。下一步我们就来创建这个时钟。

DA_SCLK是用CLK50M通过二分频电路得到的。所以其source clock为CLK50M。但是,我们在使用create_generated_clock命令创建该时钟的时候,在-source的参数里,却不能直接使用CLK50M,而必须使用CLK50M所对应的pin,即PLL1|altpll_component|auto_generated|pll1|clk[1]。这主要是因为-source参数只支持pins,ports和registers。DA_SCLK是由CLK50M通过二分频电路生成的,其代码如下:

1 reg DA_SCLK; 2 3 always @(posedge CLK50M or negedge RESET) 4 5 begin 6 7 if(~RESET) 8 9 DA_SCLK <= 1‘b0; 10 11 else 12 13 DA_SCLK <= ~DA_SCLK; 14 15 end

可以看到,本质上DA_SCLK为一个寄存器的输出,所以使用get_registers命令获取DA_SCLK。DA_SCLK是由CLK50M经二分频电路生成的,所以-divide_by的参数应该是2。综上所述,用下面的命令创建DA_SCLK:

create_generated_clock -name DA_SCLK -divide_by 2 -source [get_pins {PLL1|altpll_component|auto_generated|pll1|clk[1]}] [get_registers {DAC7512:DAC7512|DA_SCLK} ]

到此为止,DAC7512控制器中所有4个时钟都创建好了。如下图所示:

我们再看TimeQuest中Unconstrained Paths中clock Status Summary,就会发现,所有的时钟都已经被添加了约束。

Timequest Timing Analyzer进行时序分析(二)

原文:http://www.cnblogs.com/fall-li/p/4394427.html