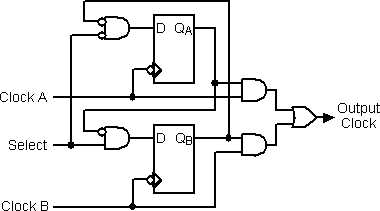

两个不相关的时钟频率之间的数字前端·异步时钟切换电路异步切换会产生runt脉冲和毛刺使得系统不可靠。下面所示的电路揭示了这些问题的一个解决办法。

当选择(SELECT)输入稳定的时候(或者为高电平或者为低电平),这两个控制触发器处于相反的状态,两个时钟输入中的一个驱动时钟输出。

当选择(SELECT)输入变化时,这个影响要等到原来的选择的时钟源的下一个下降沿复位它的控制触发器之后才会有。输出时钟信号然后会保持低电平直到新选择时钟的下一个下降沿置位它的控制触发器,使得新选择的时钟来驱动输出时钟。

任何时钟切换都开始于原来选择的时钟变低时,输出时钟然后会保持低电平直到新选择的时钟先变低然后再变高。再也不会出现runt脉冲或输出毛刺。

如果选择(SELECT)输入的时序导致控制触发器进入亚稳态,这并不会有影响,因为输出时钟被输入时钟驱动为低电平(而不管控制触发器的状态)。亚稳态必须在时钟的低电平期间内得以恢复。现代的触发器会在少于2ns时间内从亚稳态中恢复(参见2002年10月的技术报告"

Virtex-II ProTM 触发器的亚稳态时延和两次失效之间的平均时间")。

这个电路假定是上升沿触发的,它要求两个时钟都要自由运行。

异步时钟切换电路,布布扣,bubuko.com

异步时钟切换电路

原文:http://www.cnblogs.com/chenman/p/3624420.html